Interface JTAG

L'interface jtag décrite ici est utilisée, entre autres, pour la programmation in situ de CPLD et FPGA.

Le schéma électronique publié ici, a été optimisé pour un câblage et une mise en boîtier aisée. Quelques résistances accompagnées d'un 74HC244 suffisent à réaliser ce circuit. Sa connexion sur le port parallèle d'un ordinateur vous permettra de profiter pleinement des possibilités offertes par la technologie jtag.

Historique du JTAG et utilisation

Le J.T.A.G. fût fondé en 1985 à l'initiative des sociétés telles que IBM, AT&T, Texas Instrument, Philips Electronics NV, Siemens, Alcatel et Ericsson pour créer une solution de test uniforme.

Une nouvelle méthode de test, Boundary-Scan Test (BST), naquis et fut adoptée par le groupe IEEE en 1990 sous la référence standard 1149.1.

Les cellules jtag embarquées dans les composants électroniques cibles donnent à l'utilisateur la possibilité de tester ou de programmer de la mémoire FLASH, des CPLD et FPGA depuis l'apparition du « Gang Testing and In-System Programming » en mars 2000.

Maintenant, dans la pratique, nous utilisons un ou plusieurs composants ISP soudés sur une carte munie d'un port jtag à 10 broches.

Interface JTAG ou programmateur d'eeprom ?

Pour programmer les CPLD ALTERA EPM7032S ou EPM7064S nous avons à notre disposition deux méthodes.

La programmation par programmateur universel entraîne la nécessité de posséder un adaptateur PLCC44 DIL48 pour l'enficher sur le programmateur.

La programmation par le port JTAG permet de programmer toute sorte de composants programmables in situ.

Pour les CPLD et FPGA ALTERA, elle se fait à l'aide d'une interface connectée au port parallèle du PC.

Une interface jtag est un circuit électronique connecté entre la carte cible et un ordinateur pour l'opération de programmation in-situ (gestion des signaux).

Interface jtag selon ALTERA

En consultant diverses ressources sur le net on trouvera des solutions variées quant à la réalisation d'un câble JTAG.

Chacune des réalisations est motivée par l'envie de programmer tel ou tel composant ou bien de modifier le firmware d'un appareil du commerce.

Le câble ByteBlasterMV

Le câble ByteBlasterMV est la solution que le constructeur ALTERA à mise en oeuvre pour la programmation par port jtag des composants CPLD et FPGA qu'il commercialise. Ce câble est le dispositif qu'ALTERA préconise d'utiliser conjointement avec le logiciel MAX+PLUS 2 ou Quartus 2 ; il n'est ni plus ni moins qu'une interface pour port parallèle de PC.

Le schéma électronique de cette interface est disponible sur le site d'ALTERA ou sur des documentations et CD divers émanant de ce constructeur.

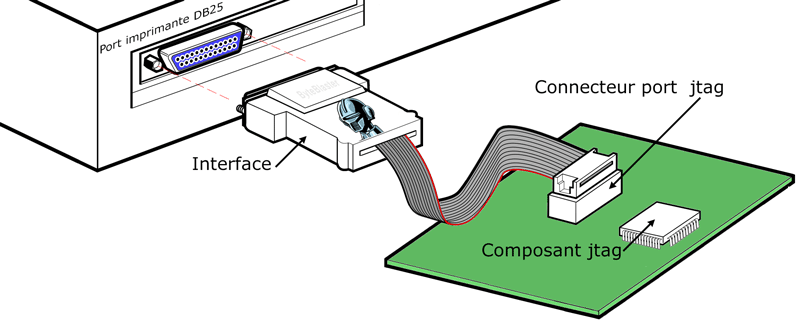

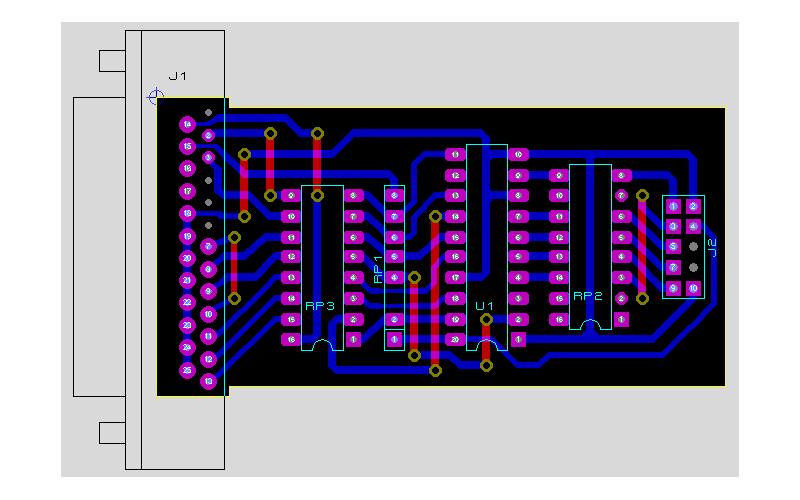

Interface pour PC se connectant sur le port imprimante avec son câble pour le port jtag.

Caractéristiques

Cette interface s'utilise sur un PC équipé d'un port parallèle 25 broches.

Elle permet la programmation in-situ des composants MAX 9000, MAX 7000S, MAX 7000A, MAX7000B, et MAX3000A.

Elle permet aussi la configuration APEX II, APEX 20K (inclus APEX 20K, APEX 20KE, and APEX 20KC), ACEX 1K, Mercury , FLEX 10K (inclus FLEX 10KA and FLEX 10KE), FLEX 8000, FLEX 6000 et les solutions processeur embarqué Excalibur.

L'alimentation en 3,3 V ou 5 V est amenée par le port jtag la carte cible.

Le téléchargement des données s'effectue à partir des logiciels MAX+PLUS 2 ou Quartus 2.

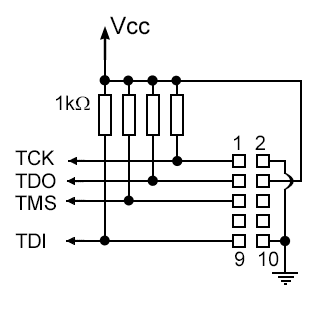

L'utilisation est faite avec un connecteur 10 broches mâles sur la carte cible.

Réalisation d'une interface

Prototype

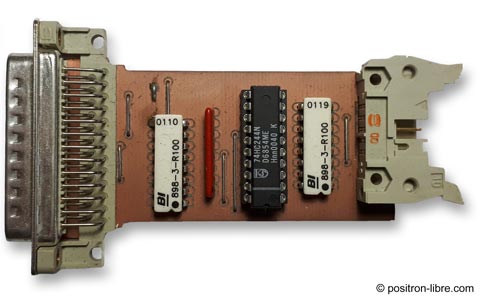

La première interface jtag présenté ici, est un prototype gravé avec une machine à commande numérique (réalisation 2001 qui fonctionne toujours).

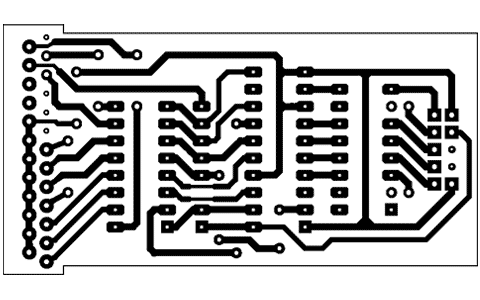

Prototype d'interface jtag dont le circuit imprimé a été réalisé en gravure mécanique (CNC).

Nous distinguons au centre le 74HC244 monter sur support tulipe. Le 74HC244 est un octuple tampon non inverseur servant également de commande de ligne à trois états. Le circuit 74HC244 est conçu pour améliorer le fonctionnement des systèmes de commande d'horloge et des émetteurs-récepteurs de bus.

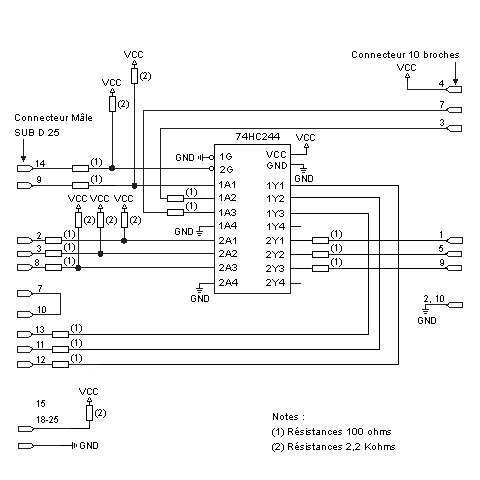

Schéma électronique

Schéma du câble ByteBlasterMV ALTERA.

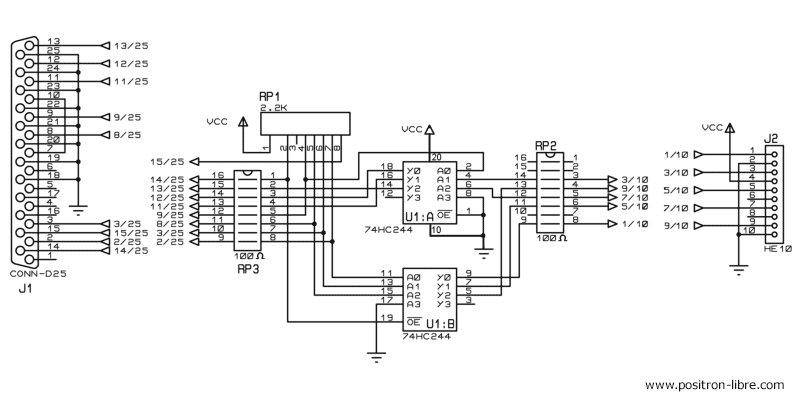

La version Positron-libre

En observant le schéma électronique ci-dessus on remarquera l'utilisation répétée des résistances de 100 Ω et 2,2 kΩ.

Dans un souci de facilité de réalisation (routage, implantation, soudage) j'ai adapté ce schéma en utilisant des réseaux de résistances dip et sip. Cette version à composants traversants (le soudage des CMS n'est pas encore à la portée de tous) n'en comporte que 4 à souder (plus les connecteurs). Les chances de se tromper sont quasi nulles (tous les composants sont orientés dans le même sens).

Ceux qui opteront pour un circuit imprimé simple face implanteront les ponts de câblage (conducteurs remplaçant les pistes côté composants) avant toute chose.

Le schéma de l'interface jtag arrangé par positron-libre d'après le schéma du ByteBlaster d'ALTERA.

Routage

Le circuit est réalisable en simple face mais la version double face procure une facilité de câblage accrue.

Ci-dessous : aperçu du tracé côté cuivre vu de dessus par transparence (images non exploitables dans cet affichage).

Typon côté cuivre vue de dessus par transparence

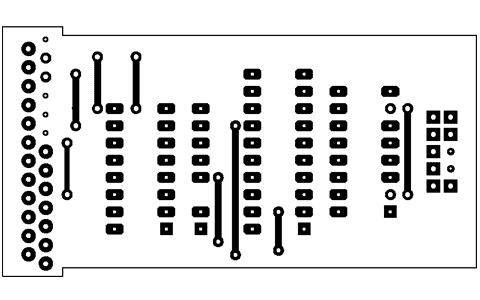

Tracé du routage côté composants vu de dessus.

Typon côté composant

Implantation des composants

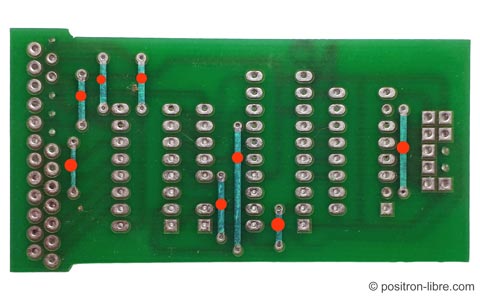

Vue de dessus du circuit imprimé : les pistes côté soudures sont vues par transparence.

Schéma d'implantation des composants de l'interface jtag vue de dessus. Nous pouvons noter l'absence de pastille pour la patte trois du réseau de résistance RP1.

Liste des composants

- 1 support DIL tulipe 20 pins,

- 2 réseaux de résistances DIL 8 fois 100 Ω (RP2 et RP3),

- 1 réseau de résistances SIL 7 fois 2,2 kΩ (RP1),

- 1 circuit intégré 74HC244,

- 1 embase HE10 2 fois 5 contacts (10 points),

- 1 connecteur DB25 mâle à souder sur CI, couder à 90° (sans vis),

- un boîtier ou capot pour DB25,

- 2 connecteurs HE10 femelle 10 points,

- 30 cm de nappe 10 conducteurs (vous pouvez aussi acheter une nappe toute faite),

- éventuellement une rallonge port imprimante (câblée complète c'est mieux).

Note : la carte électronique supportant les composants programmables in-situ sera équipée d'un connecteur mâle 10 points pour la réalisation du port jtag (voir schéma ci-dessous).

Schéma électronique pour exploitation du port jtag.

Construction de l'adaptateur

Étape 1

Implantez et soudez les 8 ponts de câblage si votre CI est en simple face.

Les straps de câblage sont représentés en rouge sur le plan d'implantation (piste verticales face composant).

Vue du dessus du circuit côté composants. Les pistes qui remplacent les ponts de câblage sont identifiées avec un point rouge.

Étape 2

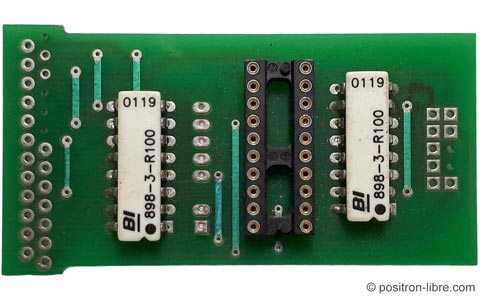

Soudez les deux réseaux de résistance DIL RP2 et RP3.

Soudez le support de CI type tulipe 20 broches.

Implantation et soudage des composants DIL.

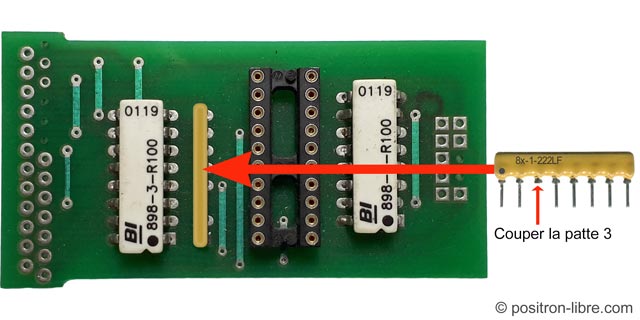

Étape 3

Coupez la troisième patte du réseau de résistance SIL RP1 (2,2 kΩ) puis soudez le composant dans la bonne orientation.

Implantation et soudage du réseau de 7 résistances SIL après avoir coupé la troisième patte.

Si vous ne trouvez pas de réseaux à 7 résistances, vous pouvez couper la 9e patte d'un réseau de 8 ; il y a assez de place sur le montage.

Étape 4

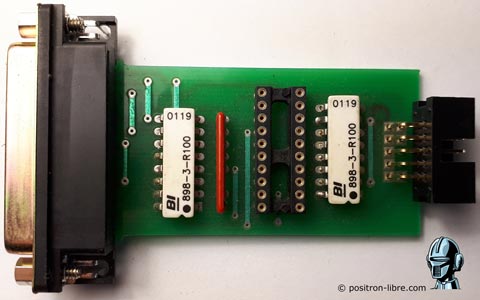

Implantez le connecteur DB25 et le connecteur HE10.

Vérifiez, avant soudage, la qualité de l'assemblage mécanique avec le boîtier.

Soudez les connecteurs et faire une vérification visuelle de toutes les soudures.

Implantation des connecteurs coudés DB25 et HE10

Implantez le 74HC244 dans son support et enfermez le tout dans son boîtier.

Implantation du circuit intégré 74HC244 dans son support et mise en boîtier de la carte.

Fabrication du câble interface carte cible

Le câble sera fabriqué avec 20 à 30 cm (pas plus) de nappe 10 conducteurs.

On sertira à chaque extrémité un connecteur HE10 femelle 2 fois 5 contacts.

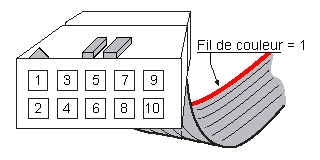

Il est important de bien faire correspondre la pin 1 du connecteur au fil 1 (couleur rouge). Il faut faire pivoter la nappe à une extrémité du câble.

Si la longueur du câble se révèle trop courte pour aller jusqu'à l'interface jtag de la carte cible, on rallongera l'ensemble avec une rallonge (de bonne qualité), pour port parallèle, intercalée entre l'interface jtag et le port parallèle du PC.

Détail du connecteur du port jtag.

Vous pouvez maintenant programmer vos circuits ISP et vous exercez sur la carte électronique à EPM7128 décrite sur ce site.

Fichiers, images et schémas

Tous les fichiers de fabrication du PCB et CAO-DAO PROTEUS, les images du typon et du schéma électronique sont disponibles à l'emplacement fichiers/electronique/montages/interfacejtag avec les informations d'exploitation.